SerDes (serializer/deserializer)

What is SerDes (serializer/deserializer)?

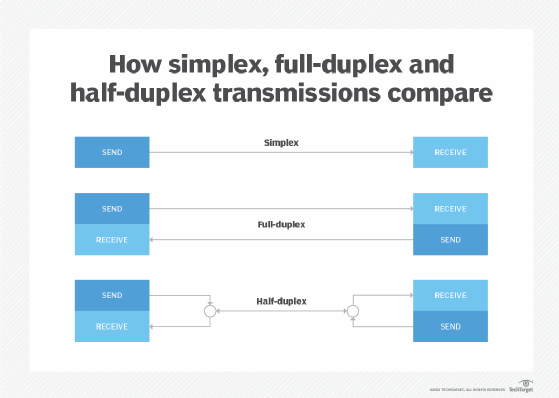

A SerDes, or serializer/deserializer, is an integrated circuit (IC or chip) transceiver that converts parallel data to serial data and vice versa. The transmitter section is a parallel-to-serial converter, and the receiver section is a serial-to-parallel converter. Most SerDes devices support full-duplex operations, meaning that data conversion can take place in both directions simultaneously.

SerDes chips facilitate data transmission between two points by converting parallel data to a serial stream before transmitting it and then converting it back to parallel data at the destination point. Converting the data this way reduces the number of data paths needed to transmit data and the number of required connecting pins or wires. It additionally addresses other issues that come with transmitting parallel data, such as greater power consumption, susceptibility to electromagnetic interference and the likelihood of clock timing skew.

SerDes design basics

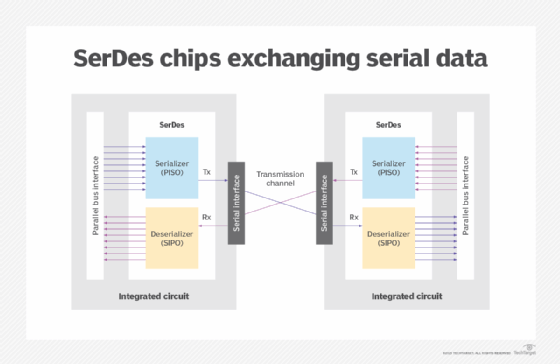

An IC can house multiple SerDes devices, and a SerDes device can house multiple lanes, with each lane handling the input and output traffic for a serial interface. Although SerDes devices can vary, they generally contain two functional blocks:

- Parallel In Serial Out (PISO). The PISO is a parallel-to-serial converter (serializer). It receives parallel data from the local system as input, converts it to serial data and outputs it as a single data stream, which is then conducted over a serial transmission channel such as coaxial or twisted-pair cable. When serializing the data, the PISO uses input from a reference clock as part of the encoding process, which minimizes the type of timing issues found in parallel transmissions.

- Serial In Parallel Out (SIPO). The SIPO is a serial-to-parallel converter (deserializer). It receives serial data as input, converts it to parallel data and outputs it as a parallel data stream, which is typically sent to a parallel bus interface connected to an integrated circuit such as a system-on-chip, field-programmable gate array or application-specific integrated circuit.

The following illustration provides a conceptual overview of two SerDes chips exchanging serial data across a serial transmission channel. Each chip includes the PISO serializer and SIPO deserializer. The serializer receives data from the parallel bus interface, converts it to serial data, and streams it to the transmission channel. At the same time, the deserializer on each SerDes receives the incoming serial stream from the other SerDes, converts it to a parallel data stream and sends it to the parallel bus interface.

A SerDes chip might also include an encoder, clock multiplier unit, physical coding sub-block, clock and data recovery unit, input and output staging areas, or other components.

One of the most important components used for serializing and deserializing data is the phase-locked loop (PLL), which is a closed-loop, feedback-control system that's both frequency and phase sensitive. The PLL generates a signal at the serial frequency that is based on the phase and frequency of the reference clock. The PISO uses the PLL signal when serializing the parallel data input. The SIPO also uses the PLL as a reference clock when deserializing data. A PLL might be internal or external to the SerDes blocks. In addition, each block might have its own PLL, or the two blocks might share the same PLL.

SerDes chips vary among vendors, depending on factors such as how they're used, the number of lanes they include and what speeds they support. Even so, chip manufacturers tend to adopt one of the following four architectures in their SerDes designs:

- Parallel clock. The SerDes embeds data address and control signals along with the parallel data input. The serial stream is outputted with an additional clock signal that is used when deserializing the data.

- Embedded clock. The SerDes embeds both the parallel data input and reference clock signal into a single serial stream. Two clock bits are embedded into the stream at every cycle to create a frame around each bitstream.

- 8b/10b. The SerDes converts each byte from the parallel data input to a 10-bit symbol (8 bits plus 2 bits) and embeds the symbols into the serial stream. The encoding scheme achieves DC balance in the serial transmission channel by limiting the disparity in the number of consecutive 0s or 1s.

- Bit interleaved. The SerDes multiplexes several slower serial streams into a single, faster stream by interleaving the bits from the input streams.

SerDes chips are used in Gigabit Ethernet systems, wireless network routers, fiber optic communication systems, storage systems, automotive components and a wide range of other environments. Many of today's SerDes devices operate at speeds in excess of 100 Gbps, with faster speeds on the horizon.